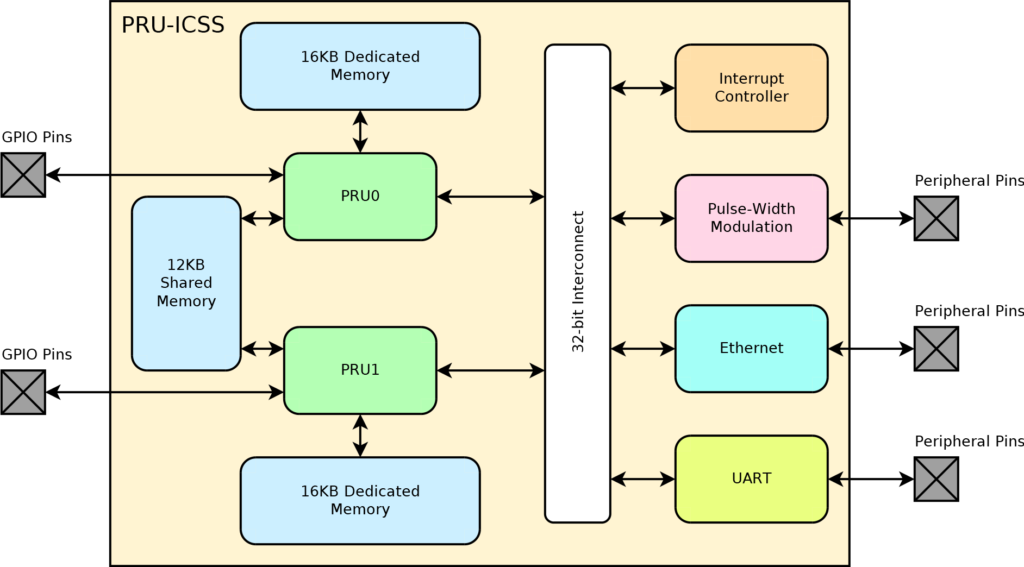

The Beaglebone AM3358 CPU includes two separate on-die co-processors called Programmable Real-Time Units (PRU). Each PRU is a 32-bit RISC processor running at 200MHz. The two PRU co-processors are part of a larger system called the Programmable Real-Time Unit Subsystem and Industrial Communication Subsystem (PRU-ICSS). The PRU-ICSS also includes a dedicated interrupt controller, pulse-width modulation subsystem, ethernet subsystem and serial port (UART). These subsystems are shared by both PRU cores. Each PRU core has access to 8KB of program storage, 8KB of data storage and 32 32-bit hardware registers. The last two registers (r30 and r31) are reserved for direct access to GPIO pins.

The PRU instruction set is designed to be minimal. It is not intended to run an OS, but rather to run real-time processes that expect minimal interruption. These processes can communicate with the CPU (which probably is running an OS) in various ways including a shared memory interface. Having the PRU co-processors on the same die as the CPU allows for high bandwidth communication between the two. The pulse-width modulation module allows the PRU to quickly adjust power to external peripherals, including stepper motors. The ethernet and UART modules can be used for direct external communication by the PRU for debugging, basic control or many other purposes. The two PRU co-processors expand the Beaglebone’s capabilities in real-time applications.